[딜사이트 심두보 기자] 초미세 공정은 반도체를 세계에서 가장 중요한 산업으로 만들었습니다. 그리고 삼성전자가 3나노 양산을 선언하면서 그 경쟁은 더욱 치열해지고 있습니다. 학계에선 2나노에서 물리적 한계에 도달하게 될 것이라고 보고 있기 때문이죠. 그러나 과거 1980년대 100나노가, 1990년대 50나노가 각각 물리적 한계로 언급됐지만, 언제나 그랬듯 그 벽은 허물어졌습니다. 그리고 3나노 시대에 접어든 지금 1나노에 대한 도전이 이뤄지는 것은 당연한 수순일지도 모릅니다.

◆옹스트롬 시대로의 진격

우리가 주목해야 할 기업은 imec입니다. 유럽 최대의 종합 반도체 연구소입니다. imec은 TSMC, 삼성전자, 인텔 등 파운드리와 ASML 등 최첨단 장비 기업 등과 공동 기술개발을 진행하죠.

이 글로벌 최고 수준의 반도체 연구기관은 2022년 5월 한 로드맵 일정을 공개했습니다. 이 로드맵에는 2036년까지 글로벌 반도체 기업들과 협력해 1나노 이하 실리콘과 트랜지스터를 개발한다는 내용이 포함되어 있죠.

imec은 2024년 2나노, 2026년 14옹스트롬에 도달하게 될 것으로 보고 있습니다. 그리고 2028년 대망의 10옹스트롬, 즉 1나노에 진입하게 되죠. 이후 2030년 7옹스트롬과 2032년 5옹스트롬, 2034년 3옹스트롬에 다다른 후 마침내 2036년 2옹스트롬에 다다를 수 있다는 로드맵이 그려지고 있습니다.

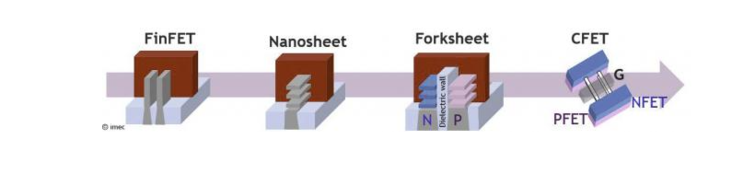

그리고 이 과정에서 더 세밀한 공정을 위해 반도체 구조 역시 바뀌게 됩니다. 3나노까지 적용됐던 FinFET 구조는 2나노대로 진입하면서 GAA 나노시트(Nanosheet)에 자리를 내어주게 됩니다. 삼성전자는 3나노 공정에서 이미 GAA 나노시트 구조를 도입했습니다. 그리고 TSMC는 2나노부터 GAA 기술을 적용할 계획이고요.

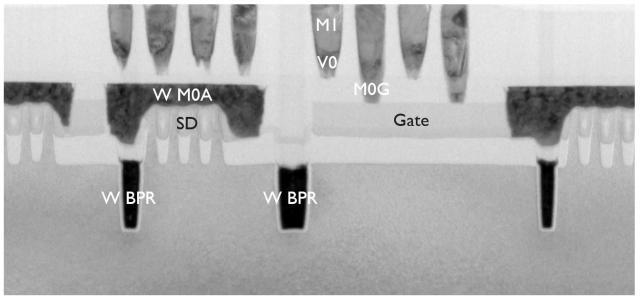

10옹스트롬, 즉 1나노부터 7옹스트롬까지는 GAA 포크시트(Forksheet) 구조가 쓰이게 될 것으로 보입니다. 이 포크시트는 N형 FET과 P형 PET의 나노시트가 긴밀하게 붙어있고, 그 중간에 절연벽을 넣는 방식입니다.

그리고 5옹스트롬부터는 CFET 구조가 활용될 것으로 imec은 보고 있습니다. 이 공정은 The Complementary FET을 의미하죠. P형 FET 위에 N형 FET을 쌓게 됩니다. 서로 다른 전도 유형의 트랜지스터를 교대로 3차원적으로 쌓아 셀 면적을 크게 낮추게 됩니다.

이 일련의 미세화 작업은 구조의 진화, 그리고 EUV의 개발이 서로 맞물리며 진행됩니다.

◆1나노를 향한 파운드리의 여정

개별 기업의 나노 로드맵을 살펴봅시다.

TSMC는 현재의 3나노 연구팀을 1.4나노 연구팀으로 전환합니다. 그리고 2024년부터 도입되는 ASML의 차세대 노광기기인 하이NA EUV를 2025년 도입되는 2나노 공정이 아닌 2027년 상용화되는 1.4나노 공정에 사용할 것이라는 보도가 있었죠. 이러한 스케줄은 imec의 로드맵과 어느 정도 일치하기도 합니다. TSMC는 수천억 원에 달하는 최첨단 EUV의 효율을 극대화하기 위해 옹스트롬 단위의 미세공정에 이를 쓴다는 큰 그림을 그리고 있는 것으로 보이고요.

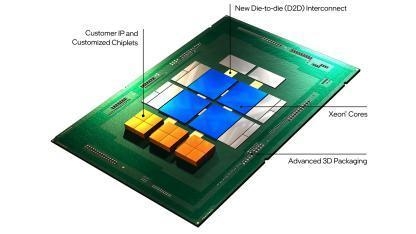

인텔은 2024년 하반기 1나노대 후반 공정으로 예상되는 인텔 18A을 준비하고 있습니다. 여기서 A는 옹트스롬을 의미하죠. 그리고 이 공정에 TSMC와 마찬가지로 하이NA EUV가 쓰일 것으로 전망되고 있습니다. 삼성전자, 그리고 TSMC와의 격차가 상당한 인텔은 10나노의 벽을 빠른 속도로 넘기 위한 시간표를 세웠죠. 이 미국의 거대 반도체 기업은 7나노급 공정인 인텔 4를 올해 하반기에, 3나노에 준하는 공정인 인텔 3을 2023년 하반기에 각각 상용화할 계획입니다. 그리고 나선 2나노 공정에는 가장 먼저 도달한다는 공격적인 목표를 수립해 두고 있죠.

이제 삼성전자입니다. 3나노 양산을 선언하며 TSMC와의 기술격차가 그리 크지 않음을 보여준 삼성전자는 아직 1나노 공정에 대해 공식적으로 계획을 밝힌 바 없습니다. 2021년 10월 삼성 파운드리 포럼 2021에서 'GAA 기술 기반 3나노 및 2나노 공정 양산 계획'을 발표했었죠. 이 한국의 반도체 기업은 2025년 GAA 기반 2나노를 양산할 수 있을 것이라고 전했습니다. 1나노에 대한 로드맵은 머지않아 열린 삼성 파운드리 포럼 2022에 나오지 않을까 추정되고 있습니다.

IBM은 2021년 12월 삼성전자와 함께 개발한 VTFET 기술을 공개했는데, 이 기술의 작동 원리는 반도체의 전류가 수직 방향으로 순환할 수 있도록 적층하는 데에 있습니다. 이 기술로 1나노 이하 공정이 가능해질 수 있다는 전망도 있죠. 적층이란 점에서 VTFET은 앞서 언급한 CFET과 유사합니다.

◆숫자, 그 너머의 영역

반도체에 집적되는 트랜지스터 수가 2년마다 2배씩 증가한다는 무어의 법칙, 다들 잘 알고 계실 텐데요. 이 법칙은 물리적·경제적 한계 때문에 폐기될 위기에 수차례 직면했죠. 하지만 그때마다 기술의 한계는 돌파됐고, 이 법칙은 여전히 유효합니다. 그리고 나노와 옹스트롬의 숫자로 표시되는 미세화 경쟁 속에서 무어의 법칙은 건재함을 보이고 있습니다.

그러나 나노나 옹스트롬의 숫자보다 더 중요한 것들이 있죠. 가장 미세한 공정이 가장 뛰어난 기술력을 의미하진 않습니다. 그리고 뛰어난 기술력이 기업의 상업적 성공을 의미하지도 않습니다. 다만 그 가능성을 가늠해 볼 수 있는 하나의 중요한 척도로 보는 게 합리적일 겁니다. 빅테크 고객의 유입, 그리고 그 고객과의 공고한 협력 관계 구축, 더 나아가 높은 비용과 긴 시간이 소요되는 칩 설계를 위한 생태계 조성 등의 이슈는 미세화의 진척만큼이나 파운드리 3사의 경쟁에 핵심적인 요소일 것입니다.

ⓒ새로운 눈으로 시장을 바라봅니다. 딜사이트 무단전재 배포금지

Home

Home